Verilog Blocking & Non-Blocking

Blocking assignment statements are assigned using = and are executed one after the other in a procedural block. However, this will not prevent execution of statments that run in a parallel block.

Note that there are two initial blocks which are executed in parallel when simulation starts. Statements are executed sequentially in each block and both blocks finish at time 0ns. To be more specific, variable a gets assigned first, followed by the display statement which is then followed by all other statements. This is visible in the output where variable b and c are 8'hxx in the first display statement. This is because variable b and c assignments have not been executed yet when the first $display is called.

In the next example, we'll add a few delays into the same set of statements to see how it behaves.

Non-blocking

Non-blocking assignment allows assignments to be scheduled without blocking the execution of following statements and is specified by a symbol. It's interesting to note that the same symbol is used as a relational operator in expressions, and as an assignment operator in the context of a non-blocking assignment. If we take the first example from above, replace all = symobls with a non-blocking assignment operator , we'll see some difference in the output.

See that all the $display statements printed 'h'x . The reason for this behavior lies in the way non-blocking assignments are executed. The RHS of every non-blocking statement of a particular time-step is captured, and moves onto the next statement. The captured RHS value is assigned to the LHS variable only at the end of the time-step.

So, if we break down the execution flow of the above example we'll get something like what's shown below.

Next, let's use the second example and replace all blocking statements into non-blocking.

Once again we can see that the output is different than what we got before.

If we break down the execution flow we'll get something like what's shown below.

Blocking vs. Nonblocking in Verilog

The concept of Blocking vs. Nonblocking signal assignments is a unique one to hardware description languages. The main reason to use either Blocking or Nonblocking assignments is to generate either combinational or sequential logic. In software, all assignments work one at a time. So for example in the C code below:

The second line is only allowed to be executed once the first line is complete. Although you probably didn’t know it, this is an example of a blocking assignment. One assignment blocks the next from executing until it is done. In a hardware description language such as Verilog there is logic that can execute concurrently or at the same time as opposed to one-line-at-a-time and there needs to be a way to tell which logic is which.

<= Nonblocking Assignment

= Blocking Assignment

The always block in the Verilog code above uses the Nonblocking Assignment, which means that it will take 3 clock cycles for the value 1 to propagate from r_Test_1 to r_Test_3. Now consider this code:

See the difference? In the always block above, the Blocking Assignment is used. In this example, the value 1 will immediately propagate to r_Test_3 . The Blocking assignment immediately takes the value in the right-hand-side and assigns it to the left hand side. Here’s a good rule of thumb for Verilog:

In Verilog, if you want to create sequential logic use a clocked always block with Nonblocking assignments. If you want to create combinational logic use an always block with Blocking assignments. Try not to mix the two in the same always block.

Nonblocking and Blocking Assignments can be mixed in the same always block. However you must be careful when doing this! It’s actually up to the synthesis tools to determine whether a blocking assignment within a clocked always block will infer a Flip-Flop or not. If it is possible that the signal will be read before being assigned, the tools will infer sequential logic. If not, then the tools will generate combinational logic. For this reason it’s best just to separate your combinational and sequential code as much as possible.

One last point: you should also understand the semantics of Verilog. When talking about Blocking and Nonblocking Assignments we are referring to Assignments that are exclusively used in Procedures (always, initial, task, function). You are only allowed to assign the reg data type in procedures. This is different from a Continuous Assignment . Continuous Assignments are everything that’s not a Procedure, and only allow for updating the wire data type.

Leave A Comment Cancel reply

Save my name, email, and website in this browser for the next time I comment.

Blocking and Non-blocking Assignment in Verilog

- Assignment is only done in procedural block(always ot initial block)

- Both combintational and sequential circuit can be described.

- Assignment can only possible to reg type irrespect of circuit type

Let's say we want to describe a 4-bit shift register in Verilog. For this, we are required to declare a 3-bit reg type variable.

The output of shift[0] is the input of shift[1], output of shift[1] is input of shift[2], and all have the same clock. Let's complete the description using both assignment operator.

Non-Blocking Assignment

When we do synthesis, it consider non-blocking assignment separately for generating a netlist. If we see register assignment in below Verilog code, all register are different if we consider non-blocking assignment separately. If you do the synthesis, it will generate 3 registers with three input/output interconnects with a positive edge clock interconnect for all register. Based on the Verilog description, all are connected sequentially because shift[0] is assigned d, shift[1] is assigned shift[0], and shift[2] is assigned shift[1].

Blocking Assignment

If we use blocking assignment and do the syhtheis, the synthesis tool first generate netlist for first blocking assignment and then go for the next blocking assignment. If in next blocking assignment, if previous output of the register is assigned to next, it will generate only a wire of previously assigned register.

In below Verilog code, even though all looks three different assignment but synthesis tool generate netlist for first blocking assigment which is one register, working on positive edge of clock, input d and output shift[0]. Since blocking assignment is used, for next blocking assignment, only wire is generated which is connected to shift[0]. Same is for next statement a wire is generated which is connected to shift[0].

Click like if you found this useful

Add Comment

This policy contains information about your privacy. By posting, you are declaring that you understand this policy:

- Your name, rating, website address, town, country, state and comment will be publicly displayed if entered.

- Your IP address (not displayed)

- The time/date of your submission (displayed)

- Administrative purposes, should a need to contact you arise.

- To inform you of new comments, should you subscribe to receive notifications.

- A cookie may be set on your computer. This is used to remember your inputs. It will expire by itself.

This policy is subject to change at any time and without notice.

These terms and conditions contain rules about posting comments. By submitting a comment, you are declaring that you agree with these rules:

- Although the administrator will attempt to moderate comments, it is impossible for every comment to have been moderated at any given time.

- You acknowledge that all comments express the views and opinions of the original author and not those of the administrator.

- You agree not to post any material which is knowingly false, obscene, hateful, threatening, harassing or invasive of a person's privacy.

- The administrator has the right to edit, move or remove any comment for any reason and without notice.

Failure to comply with these rules may result in being banned from submitting further comments.

These terms and conditions are subject to change at any time and without notice.

Comments (1)

hey in blocking assignment do we get shift in data i dont think so . we get all values same and equal to d.

Please do not focus on the module name; focus on how the netlist is generated after the synthesis.

Blocking (immediate) and Non-Blocking (deferred) Assignments in Verilog

There are Two types of Procedural Assignments in Verilog.

- Blocking Assignments

- Nonblocking Assignments

To learn more about Delay: Read Delay in Assignment (#) in Verilog

Blocking assignments

- Blocking assignments (=) are done sequentially in the order the statements are written.

- A second assignment is not started until the preceding one is complete. i.e, it blocks all the further execution before it itself gets executed.

Non-Blocking assignments

- Nonblocking assignments (<=), which follow each other in the code, are started in parallel.

- The right hand side of nonblocking assignments is evaluated starting from the completion of the last blocking assignment or if none, the start of the procedure.

- The transfer to the left hand side is made according to the delays. An intra- assignment delay in a non-blocking statement will not delay the start of any subsequent statement blocking or non-blocking. However normal delays are cumulative and will delay the output.

- Non-blocking schedules the value to be assigned to the variables but the assignment does not take place immediately. First the rest of the block is executed and the assignment is last operation that happens for that instant of time.

To learn more about Blocking and Non_Blocking Assignments: Read Synthesis and Functioning of Blocking and Non-Blocking Assignments

The following example shows interactions between blocking and non-blocking for simulation only (not for synthesis).

For Synthesis (Points to Remember):

- One must not mix “<=” or “=” in the same procedure.

- “<=” best mimics what physical flip-flops do; use it for “always @ (posedge clk..) type procedures.

- “=” best corresponds to what c/c++ code would do; use it for combinational procedures.

Spread the Word

- Click to share on Facebook (Opens in new window)

- Click to share on Twitter (Opens in new window)

- Click to share on LinkedIn (Opens in new window)

- Click to share on Pinterest (Opens in new window)

- Click to share on Tumblr (Opens in new window)

- Click to share on Pocket (Opens in new window)

- Click to share on Reddit (Opens in new window)

- Click to email a link to a friend (Opens in new window)

- Click to print (Opens in new window)

Related posts:

- Synthesis and Functioning of Blocking and Non-Blocking Assignments.

- Delay in Assignment (#) in Verilog

- Ports in Verilog Module

- Module Instantiation in Verilog

Post navigation

Leave a reply cancel reply.

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Notify me of follow-up comments by email.

Notify me of new posts by email.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| ||

| Blocking and Nonblocking Statements | ||

| ||

: A blocking statement must be executed before the execution of the statements that follow it in a sequential block. In the example below the first time statement to get executed is a = b followed by | ||

| ||

| ||

: Nonblocking statements allow you to schedule assignments without blocking the procedural flow. You can use the nonblocking procedural statement whenever you want to make several register assignments within the same time step without regard to order or dependence upon each other. It means that nonblocking statements resemble actual hardware more than blocking assignments. | ||

| ||

| block_nonblock(); 2 a, b, c, d , e, f ; 3 4 5 6 a #10 1'b1; 7 b #20 1'b0; 8 c #40 1'b1; 9 10 11 12 13 d 1'b1; 14 e 1'b0; 15 f 1'b1; 16 17 18 | ||

| ||

| ||

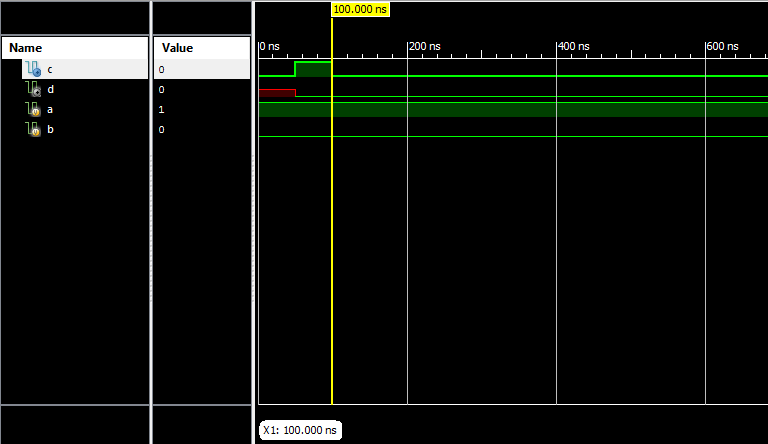

| Example - Blocking | ||

| ||

| blocking (clk,a,c); 2 clk; 3 a; 4 c; 5 6 clk; 7 a; 8 c; 9 b; 10 11 ( clk ) 12 13 b a; 14 c b; 15 16 17 | ||

| ||

| ||

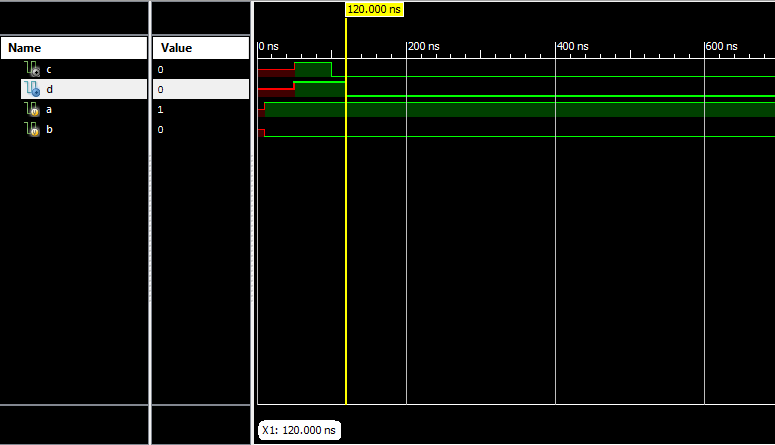

| ||

| ||

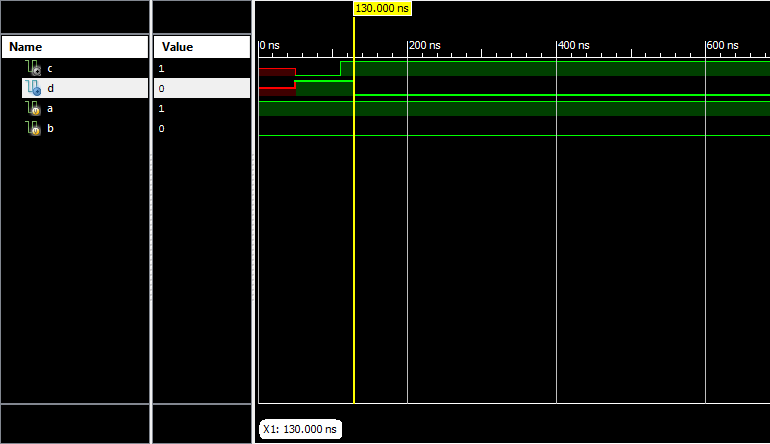

| Example - Nonblocking | ||

| ||

| nonblocking (clk,a,c); 2 clk; 3 a; 4 c; 5 6 clk; 7 a; 8 c; 9 b; 10 11 ( clk ) 12 13 b a; 14 c b; 15 16 17 | ||

| ||

| ||

| ||

| ||

| ||

| ||

|

|

|

|

|

|

|

|

|

|

|

- Getting started with verilog

- Hello World

- Procedural Blocks

- Non-blocking assignments

- Simple counter

- Synthesis vs Simulation mismatch

verilog Procedural Blocks Non-blocking assignments

Fastest entity framework extensions.

A non-blocking assignment ( <= ) is used for assignment inside edge-sensitive always blocks. Within a block, the new values are not visible until the entire block has been processed. For example:

Notice the use of non-blocking ( <= ) assignments here. Since the first assignment doesn't actually take effect until after the procedural block, the second assignment does what is intended and actually swaps the two variables -- unlike in a blocking assignment ( = ) or assignments in other languages; f1 still has its original value on the right-hand-side of the second assignment in the block.

Got any verilog Question?

- Advertise with us

- Cookie Policy

- Privacy Policy

Get monthly updates about new articles, cheatsheets, and tricks.

Verification Guide

SystemVerilog NonBlocking assignment

Nonblocking assignment.

- non-blocking assignment statements execute in parallel

- In the non-blocking assignment, all the assignments will occur at the same time. (during the end of simulation timestamp)

Nonblocking assignment example

In the below example, a and b are initialized with values 10 and 15 respectively, after that b is being assigned to a (a value will become 15), and value 20 is assigned to b. After assignment values expected in a and b are 15 and 20 respectively. but these values will get assigned only after the simulation time-stamp.

Simulator Output:

Nonblocking assignment example-2

In the below example, a and b are initialized with value 10 and 15 respectively. x<=a+b and y<=a+b+x value of x is sum of a (10) and b (15). -> x=10+15=25. value of y is sum of a (10) ,b(15) and x (0) -> became at current simulation time-stamp value of x=0. new value will get assigned at the end of current time stamp, and new value will be available only after the current time-stamp). therefore y=10+15+0=25;

❮ Previous Next ❯

- Stack Overflow for Teams Where developers & technologists share private knowledge with coworkers

- Advertising & Talent Reach devs & technologists worldwide about your product, service or employer brand

- OverflowAI GenAI features for Teams

- OverflowAPI Train & fine-tune LLMs

- Labs The future of collective knowledge sharing

- About the company Visit the blog

Collectives™ on Stack Overflow

Find centralized, trusted content and collaborate around the technologies you use most.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

Get early access and see previews of new features.

verilog always@(*) nonblocking assignment

Everywhere I have read has said, do not use the <= operator inside an always@(*) block, yet my professor did on his solutions for one of our homeworks, and he works in the industry too. What is their reasoning for saying this if it can be done?

- nonblocking

- 1 if you added some example code, you would get a better response. – Tony Cronin Commented Mar 22, 2014 at 23:50

- This has effectively been answered here: stackoverflow.com/questions/22565475/… – Chiggs Commented Mar 23, 2014 at 11:07

3 Answers 3

The short answer is that you can always use either blocking or non-blocking assignments, in any situation, as long as you understand the implications for scheduling. If you understand the scheduling model, you can use NBAs (ie. <= , which is not an 'operator' in this context) in combinatorial processes, which is what your prof has done. Note that using NBAs in combinatorial code might potentially reduce simulation speed.

The problem is that practically nobody actually understands "the implications for scheduling", so most people use guidelines instead. The guidelines you should read for using NBAs are in this paper . Ask if you don't understand it. It's too complicated to summarise, but the paper suggests not using NBAs in combinatorial code.

These are just guidelines, and lots of (knowledgeable) people don't like them. Bear in mind that guidelines only exist because the language is poorly designed and defined. Also bear in mind that people who write guidelines tend not to appreciate this, and like to think that there are good reasons for their guidelines.

In LRM, it says

"The implicit event_expression, @*, is a convenient shorthand that eliminates these problems by adding all nets and variables that are read by the statement."

In Verilog, when you are using <= non-blocking assignments and want to refer flip-flops or latches, your always@(...) sensitive list must contains edge-triggered clocking and reset signals.

To make the syntax more explicit and clear, you should use always_ff or always_latch with your clocking and reset signals, not just always @* .

- This doesn't answer the question, and the always_ stuff is SystemVerilog, not Verilog. They're unnecessary in Verilog (and SystemVerilog) unless you're doing something that you probably shouldn't be doing. – EML Commented Mar 24, 2014 at 10:08

Usually the usage of = is for combinational logic and <= for sequential logic.however, there are certain exceptions. one example is clock modeling, as described in Verilog Blocking Assignment . however, specifically for your question i believe Gotcha 30 (Nonblocking assignments in combinational logic) in 101 gotchas can explain it ( http://books.google.com/books?id=_VGghBpoK6cC&printsec=frontcover&dq=Verilog+and+SystemVerilog+Gotchas&hl=en&sa=X&ei=F9cvU_WhJYzdoASLoYHwBw&ved=0CCwQ6AEwAA#v=onepage&q=Verilog%20and%20SystemVerilog%20Gotchas&f=false )

- 1 I've got to say it - gotcha #30 ( always @(m,n) m <= m+n ) is nonsense. The real hardware oscillates, and the simulation oscillates, just as it should do. – EML Commented Mar 24, 2014 at 10:05

Your Answer

Reminder: Answers generated by artificial intelligence tools are not allowed on Stack Overflow. Learn more

Sign up or log in

Post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged verilog nonblocking or ask your own question .

- The Overflow Blog

- Scaling systems to manage all the metadata ABOUT the data

- Navigating cities of code with Norris Numbers

- Featured on Meta

- We've made changes to our Terms of Service & Privacy Policy - July 2024

- Bringing clarity to status tag usage on meta sites

- Feedback requested: How do you use tag hover descriptions for curating and do...

Hot Network Questions

- Violation of the Law of Total Expectation in the Unit Square?

- Trying to understand an attack showcased in a viral YouTube video

- How to create a extruded 4-star shape that is rotated inwards?

- Are all simple groups of order coprime to 3 cyclic? If so, why?

- Questions about best way to raise the handlebar on my bike

- How did Jason Bourne know the garbage man isn't CIA?

- MOSFETs keep shorting way below rated current

- Why would Space Colonies even want to secede?

- Can I cast True Strike, then cast Message to give someone else advantage?

- Were there mistakes in converting Dijkstra's Algol-60 compiler to Pascal?

- How to invoke italic correction in ConTeXt LMTX?

- What is the meaning of "Exit, pursued by a bear"?

- Caulking Bathtub and Wall Surround to prevent water leak

- Is there any point "clean-installing" on a brand-new MacBook?

- A study on the speed of gravity

- Output of a Diffractometer

- Can police offer an “immune interview”?

- Why was I was allowed to bring 1.5 liters of liquid through security at Frankfurt Airport?

- Non-linear recurrence for rational sequences with generating function with radicals?

- Is my encryption format secure?

- "Heads cut off" or "souls cut off" in Rev 20:4?

- Repeats: Simpler at the cost of more redundant?

- What are these commands in the code?

- What is this houseplant with a red fleshy stem and thick waxy leaves?

Stack Exchange Network

Stack Exchange network consists of 183 Q&A communities including Stack Overflow , the largest, most trusted online community for developers to learn, share their knowledge, and build their careers.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

Verilog non-blocking assignments

Consider the following Verilog snippet:

In my textbook it says

A group of blocking assignments are evaluated in the order they appear in the code, whilst a group of nonblocking assignments are evaluated concurrently, before any of the statements on the left hand sides are updated.

So what does that mean here? Suppose c = 1100 , a = 11 and b = 01 at the beginning. The first statement will read as c = 0011 and the second as c[0] = 0 because the c in the second statement is 1100 since the assignments only take effect after the clock cycle if I understood the textbook correctly. But what is c in the end? Is it 1100 because of the last statement, or is it 0010 ? Please also explain why.

Both statements assign a value to c[0] , so even with nonblocking assignment, it is the last statement that prevails. This means that |b in the first statement is discarded, and the result will be 0010 . The first three bits come from the first statement, and the last bit comes from the second statement, all updated simultaneously.

It could be written as a single, less confusing statement:

Your Answer

Sign up or log in, post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged verilog or ask your own question .

- The Overflow Blog

- Scaling systems to manage all the metadata ABOUT the data

- Navigating cities of code with Norris Numbers

- Featured on Meta

- We've made changes to our Terms of Service & Privacy Policy - July 2024

- Bringing clarity to status tag usage on meta sites

Hot Network Questions

- How to cite a book if only its chapters have DOIs?

- Violation of the Law of Total Expectation in the Unit Square?

- Would donations count as revenue from a free software?

- Convert a Dataset into a list of lists and back to a Dataset

- Why does the definition of a braided monoidal category not mention the braid equation?

- Can I cast True Strike, then cast Message to give someone else advantage?

- Caulking Bathtub and Wall Surround to prevent water leak

- If Venus had a sapient civilisation similar to our own prior to global resurfacing, would we know it?

- Will the US Customs be suspicious of my luggage if i bought a lot of the same item?

- Car LED circuit

- What does it mean to have a truth value of a 'nothing' type instance?

- Unexpected behaviour during implicit conversion in C

- Cleveref, biblatex and automatic equation numbering

- What is the purpose of toroidal magnetic field in tokamak fusion device?

- What connotation does "break out the checkbook" have?

- Next Bitcoin Core client version

- Do "Whenever X becomes the target of a spell" abilities get triggered by counterspell?

- How do you "stealth" a relativistic superweapon?

- Did the United States have consent from Texas to cede a piece of land that was part of Texas?

- I submitted a paper and later realised one reference was missing, although I had written the authors in the body text. What could happen?

- Venus’ LIP period starts today, can we save the Venusians?

- Erase the loops

- Terminal autocomplete (tab) not completing when changing directory up one level (cd ../)

- Might my prime lens be broken?

IMAGES

COMMENTS

The RHS of every non-blocking statement of a particular time-step is captured, and moves onto the next statement. The captured RHS value is assigned to the LHS variable only at the end of the time-step. Simulation Log. ncsim> run. [0] a= 0xx b= 0xx c= 0xx. [0] a= 0xx b= 0xx c= 0xx. [0] a= 0xx b= 0xx c= 0xx.

The Blocking assignment immediately takes the value in the right-hand-side and assigns it to the left hand side. Here's a good rule of thumb for Verilog: In Verilog, if you want to create sequential logic use a clocked always block with Nonblocking assignments. If you want to create combinational logic use an always block with Blocking ...

I. Blocking vs. Nonblocking Assignments • Verilog supports two types of assignments within always blocks, with subtly different behaviors. • Blocking assignment: evaluation and assignment are immediate • Nonblocking assignment: all assignments deferred until all right-hand sides have been evaluated (end of simulation timestep)

A big reason for following the rule of thumb and not mixing blocking and nonblocking assignments within an always block, is that mixing your assignments can cause serious simulation mismatches between RTL sims and gate-sims/real hardware operation. The verilog simulator treats = and <= quite differently. Blocking assignments mean 'assign the ...

The output of an assign statement is always equal to the specified function of it's inputs. "blocking" and "nonblocking" assignments only exist within always blocks. A blocking assignment takes affect immediately it is processed. A nonblocking assignment takes place at the end of processing the current "time delta".

Blocking and Non-blocking Assignment in Verilog. When working with behavioural modeling in Verilog, there are two types of assigment which is known as blocking and non blocking assigment and both of them there is a operator, '=' operator for blocking assignment and '=' operator for non blocking assigment.At short, blocking assignment executes one by one sequentially and non-blocking assignemnt ...

An edge-sensitive intra-assignment timing control permits a special use of the repeat loop. The edge sensitive time control may be repeated several times before the delay is completed. Either the blocking or the non-blocking assignment may be used. always always @(IN) @(IN) OUT OUT <= <= repeat.

Non-Blocking assignments. Nonblocking assignments (<=), which follow each other in the code, are started in parallel. The right hand side of nonblocking assignments is evaluated starting from the completion of the last blocking assignment or if none, the start of the procedure. The transfer to the left hand side is made according to the delays.

Blocking And Nonblocking In Verilog. Blocking Statements: A blocking statement must be executed before the execution of the statements that follow it in a sequential block. In the example below the first time statement to get executed is a = b followed by. Nonblocking Statements: Nonblocking statements allow you to schedule assignments without ...

Verilog nonblocking assignments can also be evaluated and LHS updates scheduled. The nonblocking assignment does not block other Verilog statements from being evaluated. Execution of nonblocking assignments can be viewed as a two-step process: 1. Evaluate the RHS of nonblocking statements at the beginning of the time step. 2.

A nonblocking assignment is a Verilog procedural assignment that uses the "<=" operator inside of a procedural block. It is illegal to use a nonblocking assignment in a continuous assignment statement or in a net declaration. A nonblocking assignment can be viewed as a 2-step assignment. At the beginning of a simulation

The significance of blocking and non-blocking assignments in Verilog coding cannot be overstated. These elements serve as the foundation for precise and effective digital circuit design, offering ...

end. There are now two extra states and an else. The else is needed because two dependent blocking assign-ments happen in the first clock cycle, except when the input is 2. In that case, there is only one assignment (of the input to the output). As discussed earlier, equiva-lent non-blocking code requires an if else.

Example #. A non-blocking assignment ( <=) is used for assignment inside edge-sensitive always blocks. Within a block, the new values are not visible until the entire block has been processed. For example: module flip(. input clk, input reset. ) reg f1;

Modeling the Arbiter in Verilog. • Identify the combinational and sequential components. • Express each component as a combinational or sequential always block. Arbiter Next State Always Block. Use this combinational always block to implement state transition logic with case and if- then-else constructs. 11.

always @ (pos edge clk) begin. x<=y; y<=z; end. In this non-blocking assignment immediately after rising transition of the clk signal, x=y and y=z, but x!=z. Synthesis for this code would typically create a register for x and a register for y. Where blocking assignments often are synthesized as logic. Verilog.

Nonblocking assignment example. In the below example, a and b are initialized with values 10 and 15 respectively, after that b is being assigned to a (a value will become 15), and value 20 is assigned to b. After assignment values expected in a and b are 15 and 20 respectively. but these values will get assigned only after the simulation time ...

of other Verilog nonblocking assignments can also be evaluated and LHS updates scheduled. The nonblocking assignment does not block other Verilog statements from being evaluated. Execution of nonblocking assignments can be viewed as a two-step process: 1. Evaluate the RHS of nonblocking statements at the beginning of the time step. 2.

In Verilog, when you are using <= non-blocking assignments and want to refer flip-flops or latches, your always@(...) sensitive list must contains edge-triggered clocking and reset signals. To make the syntax more explicit and clear, you should use always_ff or always_latch with your clocking and reset signals, not just always @*. This doesn't ...

Consider the following Verilog snippet: always @ ( posedge clk) begin. c <= {c, &a, |b}; c[0] <= ^c[3:2]; end. In my textbook it says. A group of blocking assignments are evaluated in the order they appear in the code, whilst a group of nonblocking assignments are evaluated concurrently, before any of the statements on the left hand sides are ...